# **Description**

The µPD27C1000A is a 1,048,576-bit ultraviolet erasable and electrically programmable read-only memory fabricated with double-polysilicon CMOS technology for a substantial savings in both operating and standby power. The device is organized as 131,072 words by 8 bits and operates from a single +5-volt power supply.

The  $\mu$ PD27C1000A has both page and single-location programming features, three-state outputs, and fully TTL-compatible inputs and outputs. It also has a program voltage (V<sub>PP</sub>) of 12.5 volts and is available in a 32-pin cerdip with a quartz window.

### **Features**

- ☐ 131,072-word by 8-bit organization

- ☐ Ultraviolet erasable and electrically programmable

- ☐ High-speed programming capability

- Page programming

- Single byte programming

- ☐ Low power dissipation

- 40 mA maximum (active)

- 100 µA maximum (standby)

- ☐ TTL-compatible I/O for reading and programming

- ☐ Single +5-volt power supply

- ☐ Double-polysilicon CMOS technology

- ☐ 32-pin cerdip packaging

- ☐ Pinout compatibility with 28-pin, mask-programmable µPD23C1000s

# **Ordering Information**

| Part Number      | Access<br>Time (max) | Package              |

|------------------|----------------------|----------------------|

| μPD27C10i)0AD-12 | 120 ns               | 32-pin cerdip with a |

| D-15             | 150 ns               | quartz window        |

| D-20             | 200 ns               |                      |

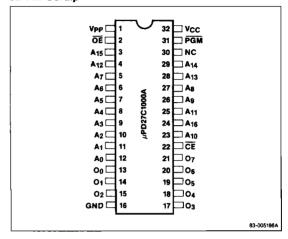

## Pin Identification

| Symbol                          | Function             |  |

|---------------------------------|----------------------|--|

| A <sub>0</sub> -A <sub>16</sub> | Address inputs       |  |

| 0 <sub>0</sub> -0 <sub>7</sub>  | Data outputs         |  |

|                                 | Chip enable          |  |

| ŌE                              | Output enable        |  |

| PGM                             | Program              |  |

| GND                             | Ground               |  |

| v <sub>cc</sub>                 | +5-volt power supply |  |

| V <sub>PP</sub>                 | Program voltage      |  |

| NC                              | No connection        |  |

# **Pin Configuration**

### 32-Pin Cerdip

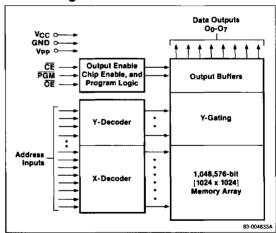

# **Block Diagram**

# **Absolute Maximum Ratings**

| Power supply voltage, V <sub>CC</sub>   | -0.6 to +7.0 V  |

|-----------------------------------------|-----------------|

| Input voltage, V <sub>IN</sub>          | -0.6 to +7.0 V  |

| Input voltage, A <sub>9</sub>           | -0.6 to +13.5 V |

| Output voltage, V <sub>OUT</sub>        | -0.6 to +7.0 V  |

| Operating temperature, T <sub>OPR</sub> | -10 to +80°C    |

| Storage temperature, T <sub>STG</sub>   | −65 to +125°C   |

| Program voltage, V <sub>PP</sub>        | -0.6 to +13.5 V |

Comment: Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

# Capacitance

TA =25°C; f = 1 MHz

|                    | Limits           |     |     |     |      |                        |

|--------------------|------------------|-----|-----|-----|------|------------------------|

| Parameter          | Symbol           | Min | Тур | Max | Unit | Test Conditions        |

| Input capacitance  | CiN              |     |     | 14  | pF   | V <sub>IN</sub> = 0 V  |

| Output capacitance | C <sub>OUT</sub> |     |     | 16  | рF   | V <sub>0UT</sub> = 0 V |

# **Truth Table**

| Mode            | Œ               | ŌĒ              | PGM<br>(Note 2) | V <sub>PP</sub> | VCC    | Outputs          |

|-----------------|-----------------|-----------------|-----------------|-----------------|--------|------------------|

| Read            | VIL             | VIL             | V <sub>IH</sub> | +5.0 V          | +5.0 V | D <sub>OUT</sub> |

| Output disable  | V <sub>IL</sub> | ViH             | Х               | +5.0 V          | +5.0 V | High-Z           |

| Standby         | VIH             | Х               | Х               | +5.0 V          | +5.0 V | High-Z           |

| Page data latch | VIH             | VIL             | V <sub>IH</sub> | +12.5 V         | +6.5 V | D <sub>IN</sub>  |

| Page program    | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | +12.5 V         | +6.5 V | High-Z           |

| Program verify  | VIL             | VIL             | V <sub>IH</sub> | +12.5 V         | +6.5 V | D <sub>OUT</sub> |

| Byte program    | VIL             | V <sub>iH</sub> | V <sub>IL</sub> | +12.5 V         | +6.5 V | D <sub>IN</sub>  |

| Program inhibit | Х               | VIL             | VIL             | +12.5 V         | +6.5 V | High-Z           |

|                 | X               | V <sub>IH</sub> | V <sub>IH</sub> |                 |        |                  |

### Notes:

- (1) ' X" can be either  $V_{IL}$  or  $V_{1H}$ .

- (2) In read operation, <del>PGM</del> must be set to V<sub>IH</sub> at all times or switched from V<sub>IL</sub> to V<sub>IH</sub> at least 2 µs before <del>OE</del> or <del>CE</del> becomes V<sub>IH</sub>.

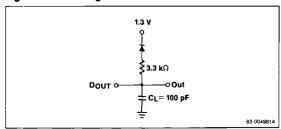

Figure 1. Loading Conditions Test Circuit

### **DC Characteristics**

$T_A = 0 \text{ to } +70 \,^{\circ}\text{C}; V_{CC} = +5.0 \text{ V} \pm 10\%; V_{PP} = V_{CC} \pm 0.6$

|                                              | Limits            |                        |                           |         |                                                                                                          |  |  |  |  |

|----------------------------------------------|-------------------|------------------------|---------------------------|---------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameter                                    | Symbol            | Min                    | Typ Max                   | Unit    | Test Conditions                                                                                          |  |  |  |  |

| Read, Output                                 | Disable,          | and                    | Standby                   | Mode    | 8                                                                                                        |  |  |  |  |

| Output voltage,                              | V <sub>DH1</sub>  | 2.4                    |                           | ٧       | $I_{OH} = -400 \mu\text{A}$                                                                              |  |  |  |  |

| high                                         | V <sub>OH2</sub>  | V <sub>CC</sub><br>0.7 |                           | ٧       | $I_{0H} = -100 \mu\text{A}$                                                                              |  |  |  |  |

| Output voltage,<br>low                       | V <sub>OL</sub>   |                        | 0.45                      | V       | $I_{0L} = 2.1 \text{ mA}$                                                                                |  |  |  |  |

| Input voltage,<br>high                       | V <sub>IH</sub>   | 2.0                    | V <sub>CC</sub> + 0.3     | 3 V     | ·                                                                                                        |  |  |  |  |

| Input voltage,<br>low                        | V <sub>IL</sub>   | -0.3                   | 0.8                       | ν       |                                                                                                          |  |  |  |  |

| Output leakage<br>current                    | lΓO               | -10                    | 10                        | μA      | $ \overline{OE} = V_{IH}; $ $ V_{OUT} = 0 \text{ V to} $ $ V_{CC} $                                      |  |  |  |  |

| Input leakage current                        | 1[[               | _<br>-10               | 10                        | μΑ      | $V_{IN} = 0 V to V_{CC}$                                                                                 |  |  |  |  |

| Operating supply current                     | I <sub>CCA1</sub> |                        | 15                        | mA      | $\overline{CE} = V_{IL};$ $V_{IN} = V_{IH}$                                                              |  |  |  |  |

|                                              | I <sub>CCA2</sub> |                        | 40                        | mA      | $ f = 8.4 \text{ MHz}; $ $ t_{ACC} = 120 \text{ ns}; $ $ l_{OUT} = 0 \text{ mA} $                        |  |  |  |  |

|                                              |                   |                        | 30                        | mA      | f = 6.7  MHz;<br>$t_{ACC} = 150 \text{ ns};$<br>$t_{OUT} = 0 \text{ mA}$                                 |  |  |  |  |

|                                              |                   |                        | 25                        | mA      | $\begin{split} f &= 5 \text{ MHz;} \\ t_{ACC} &= 200 \text{ ns;} \\ t_{OUT} &= 0 \text{ mA} \end{split}$ |  |  |  |  |

| Standby supply                               | I <sub>CCS1</sub> |                        | 1                         | mΑ      | CE = V <sub>IH</sub>                                                                                     |  |  |  |  |

| current                                      | I <sub>CCS2</sub> |                        | 1 100                     | μΑ      | $\overline{CE} = V_{CC}; V_{IN}$<br>= 0 V to $V_{CC}$                                                    |  |  |  |  |

| Program voltage current                      | Ірр               |                        | 1 100                     | μΑ      | $V_{PP} = V_{CC}$                                                                                        |  |  |  |  |

| All Program I<br>T <sub>A</sub> = +25 ±5 °C; |                   | 5 ±0.2                 | 25 V; V <sub>PP</sub> ≈ - | ⊦12.5 ± | ±0.3 V                                                                                                   |  |  |  |  |

| Output voltage,<br>high                      | V <sub>OH</sub>   | 2.4                    |                           | ٧       | $t_{OH} = -400 \mu\text{A}$                                                                              |  |  |  |  |

| Output voltage,<br>low                       | V <sub>OL</sub>   |                        | 0.45                      | ٧       | $I_{OL} = 2.1 \text{ mA}$                                                                                |  |  |  |  |

| Input voltage,<br>high                       | VIH               | 2.4                    | V <sub>CC</sub> + 0.3     | 3 V     |                                                                                                          |  |  |  |  |

| Input voltage,<br>low                        | VIL               | -0.3                   | 0.8                       | ٧       |                                                                                                          |  |  |  |  |

| Input leakage current                        | ILI               | -10                    | 10                        | μΑ      | $V_{IN} = V_{IL}$ or $V_{IH}$                                                                            |  |  |  |  |

| Operating supply current                     | lcc               |                        | 30                        | mA      |                                                                                                          |  |  |  |  |

| Program voltage current                      | Ірр               |                        | 50                        | mA      | CE = PGM =<br>V <sub>IL</sub>                                                                            |  |  |  |  |

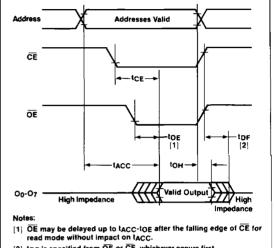

# **AC Characteristics**

$T_A = 0 \text{ tc } +70 \text{ °C}; V_{CC} = +5.0 \text{ V} \pm 10\%; V_{PP} = V_{CC}$

| Parameter                                |                 | Limits         |     |                |     |                |     |      |                                                             |

|------------------------------------------|-----------------|----------------|-----|----------------|-----|----------------|-----|------|-------------------------------------------------------------|

|                                          |                 | μP027C1000A-12 |     | μPD27C1000A-15 |     | μP027C1000A-20 |     |      |                                                             |

|                                          | Symbol          | Min            | Max | Min            | Max | Min            | Max | Unit | Test Conditions                                             |

| Read and Standby Modes                   |                 |                |     |                |     |                |     |      |                                                             |

| Address to output delay                  | tacc            |                | 120 |                | 150 |                | 200 | ns   | CE = OE = V <sub>IL</sub>                                   |

| CE to output delay                       | t <sub>CE</sub> |                | 120 |                | 150 |                | 200 | ns   | 0E = V <sub>IL</sub>                                        |

| OE to output delay                       | toE             |                | 70  |                | 70  |                | 75  | ns   | CE = V <sub>IL</sub>                                        |

| OE or CE nigh to data output float delay | t <sub>DF</sub> | 0              | 50  | 0              | 50  | 0              | 60  | ns   | $\overline{CE} = V_{IL} \text{ or } \overline{OE} = V_{II}$ |

| Address to output hold time              | toH             | 0              |     | 0              |     | 0              |     | ns   | $\overline{CE} = \overline{OE} = V_{IL}$                    |

#### Notes:

See figure 1 for output load; input rise and fall times ≤ 20 ns; input pulse levels = 0.45 V and 2.4 V; input and output timing measurement levels = 0.8 V and 2.0 V.

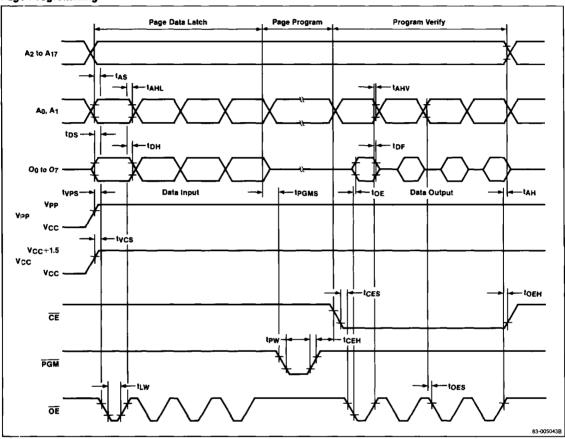

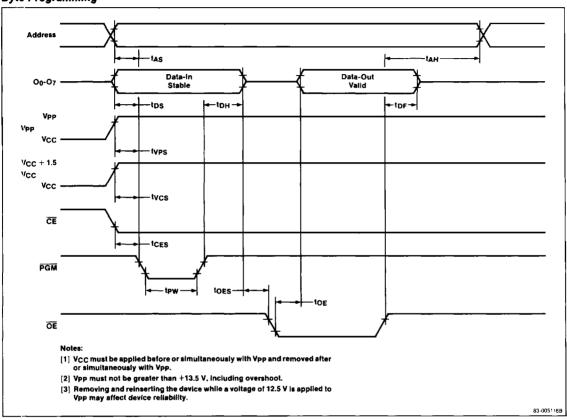

# AC Characteristics (cont)

$T_A = +25 \pm 5$  °C;  $V_{CC} = +6.5 \pm 0.25$  V;  $V_{PP} = +12.5 \pm 0.3$  V

|                                           |                  | Limits |     |       |      | Test Conditions |

|-------------------------------------------|------------------|--------|-----|-------|------|-----------------|

| Parameter                                 | Symbol           | Min    | Тур | Max   | Unit | (Note 1)        |

| Page Data La<br>and Program               |                  |        |     | Prog  | gram | Verify,         |

| Address setup<br>time                     | tas              | 2      |     |       | μS   |                 |

| Data setup time                           | t <sub>DS</sub>  | 2      |     |       | μS   |                 |

| Address hold<br>time                      | t <sub>AH</sub>  | 2      |     |       | μS   |                 |

|                                           | tAHL             | 2      |     |       | μS   |                 |

|                                           | t <sub>AHV</sub> | 0      |     |       | μS   |                 |

| Data hold time                            | t <sub>DH</sub>  | 2      |     |       | μS   |                 |

| Output enable<br>to output<br>float delay | t <sub>DF</sub>  | 0      |     | 130   | ns   |                 |

| V <sub>PP</sub> setup time                | t <sub>VPS</sub> | 2      |     |       | μS   |                 |

| Program pulse<br>width                    | tpw              | 0.095  | 0.1 | 0.105 | ms   |                 |

| V <sub>CC</sub> setup time                | tvcs             | 2      |     |       | μS   |                 |

| OE setup time                             | t <sub>OES</sub> | 2      |     |       | μS   |                 |

| 0E hold time                              | t <sub>OEH</sub> | 2      |     |       | μS   |                 |

| CE hold time                              | <sup>†</sup> CEH | 2      |     |       | μS   |                 |

| OE pulse width<br>during data<br>latch    | t <sub>LW</sub>  | 1      |     |       | μS   |                 |

| PGM setup time                            | tpgms            | 2      |     |       | μS   |                 |

| CE setup time                             | t <sub>CES</sub> | 2      |     |       | μS   |                 |

| Data valid<br>from OE                     | t <sub>OE</sub>  |        |     | 150   | ns   |                 |

|                                |                  |       |     |       | Test Cenditions |          |

|--------------------------------|------------------|-------|-----|-------|-----------------|----------|

| Parameter                      | Symbol           | Min   | Тур | Max   | Unit            | (Note 1) |

| Byte Program                   | nming N          | lode  |     |       |                 |          |

| Address setup<br>time          | t <sub>AS</sub>  | 2     |     |       | μS              |          |

| OE setup time                  | toes             | 2     |     |       | μS              |          |

| Data setup<br>time             | t <sub>DS</sub>  | 2     |     |       | μS              |          |

| Address hold time              | <sup>t</sup> AH  | 2     |     |       | μS              |          |

| Data hold<br>time              | <sup>‡</sup> DH  | 2     |     |       | μS              |          |

| OE to output<br>float time     | t <sub>DF</sub>  | 0     |     | 130   | ns              |          |

| V <sub>PP</sub> setup time     | typs             | 2     |     |       | μS              |          |

| V <sub>CC</sub> setup time     | tvcs             | 2     |     |       | μS              |          |

| Initial program<br>pulse width | tpw              | 0.095 | 0.1 | 0.105 | ms              |          |

| CE setup time                  | t <sub>CES</sub> | 2     |     |       | μS              |          |

| OE to output<br>delay          | t <sub>OE</sub>  |       |     | 150   | ns              |          |

#### Notes:

Input pulse levels = 0.45 V to 2.4 V; input and output timing reference levels = 0.8 V and 2.0 V; input rise and fall times ≤ 20 ns. See figure 1 for output load.

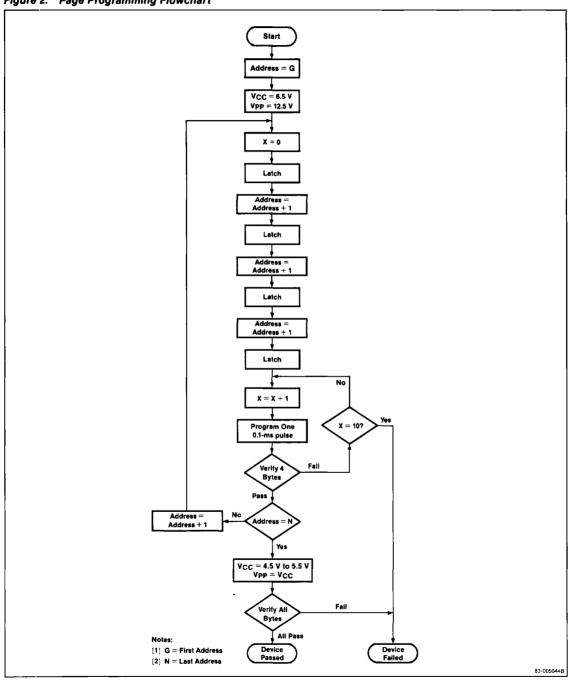

# **Programming Operation**

Begir programming by erasing all data; this sets all bits at a high logic level (1). The  $\mu$ PD27C1000A is originally shipped in this condition. To enter data, program a low-level (0) TTL signal into the chosen location.

Address the first byte or page location and apply valid data at the eight output pins. Raise  $V_{CC}$  to  $+6.5\pm0.25$  V; then raise  $V_{PP}$  to  $+12.5\pm0.3$  V.

### **Byte Programming**

For byte programming,  $\overline{CE}$  should be set at 0 and  $\overline{OE}$  at 1 to start programming at the initial address. Apply a 0.1-ms program pulse to  $\overline{PGM}$  as shown in the byte programming portion of the timing waveforms. Set  $\overline{OE}$  to 0 to verify the eight bits prior to making a program/no program decision. If the byte is not programmed, apply another 0.1-ms pulse to  $\overline{PGM}$ , up to a maximum of 10 times, and input the next address. If the bits are not programmed in 10 tries, reject the device as a program failure.

After all addresses are programmed, lower both  $V_{CC}$  and  $V_{PP}$  to +5.0 V  $\pm 10\%$  and verify all data again.

### Page Programming

For page programming,  $\overline{CE}$  and  $\overline{PGM}$  should be set to 1.  $\overline{OE}$  pulses low four times to latch the addressed 4-byte, one-page data. Subsequently,  $\overline{CE}$  and  $\overline{OE}$  should be set to a high level and a 0.1-ms program pulse applied to  $\overline{PGM}$  as shown in the page programming portion of the timing waveforms. Verify the data prior to making a program/no program decision. If all four bytes of page data are not programmed, apply another 0.1-ms pulse to  $\overline{PGM}$ , up to a maximum of 10 times, and input the next page address. If the page is not programmed in 10 tries, reject the device as a program failure.

After all addresses are programmed, lower both  $V_{CC}$  and  $V_{PP}$  to  $\pm 5.0$  V  $\pm 10\%$  and verify all data again.

### **Program Inhibit**

Use the programming inhibit option to program multiple  $\mu$ PD27C1000As connected in parallel. All like inputs except  $\overline{PGM}$  and  $\overline{OE}$  may be common. Program individual devices by applying a low-level TTL pulse to the  $\overline{PGM}$  pin of the device to be programmed. Applying a high-level signal to the  $\overline{PGM}$  pins of the other devices prevents them from being programmed.

### **Program Verification**

To verify that the device is correctly programmed, normal read operation can be used with a logic level 1 applied to the PGM pin and a logic level 0 applied to the CE and OE pins of the device to be verified. A logic level 1 should be applied to the CE and OE pins of all other devices.

#### Erasure

Erase data on the  $\mu$ PD27C1000A by exposing it to light with a wavelength shorter than 400 nm. Since exposure to direct sunlight or room-level fluorescent light could also erase the data, mask the window to prevent unintentional erasure by ultraviolet rays. Opaque labels are supplied with every device.

Data s typically erased by ultraviolet rays with a wavelength of 254 nm. A minimum integrated dose of 15 W-sec/cm<sup>2</sup> (ultraviolet lighting intensity multiplied by exposure time) is required to completely erase written data.

An ultraviolet lamp rated at 12,000 µW/cm2 takes approximately 15 to 20 minutes to complete erasure. Place the µPD27C1000A within 2.5 cm of the lamp tubes and remove any filter on the lamp.

## **Timing Waveforms**

### Read Cycle

[2] 1DF is specified from  $\overline{\text{OE}}$  or  $\overline{\text{CE}}$ , whichever occurs first.

83-004835A

# **Timing Waveforms (cont)**

# Page Programming

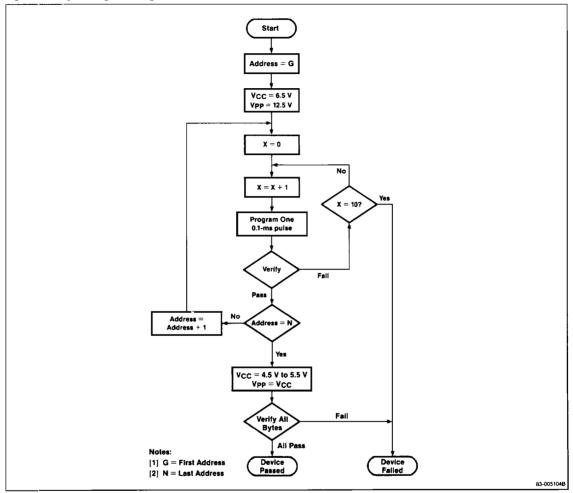

Figure 2. Page Programming Flowchart

# **Timing Waveforms (cont)**

# Byte Programming

Figure 3. Byte Programming Flowchart